一文了解芯片生产工艺流程

在当今数字化的世界里,从智能手机、个人电脑到汽车和家用电器,几乎所有电子设备的核心都离不开一个微小而强大的部件——芯片,也称为集成电路(Integrated Circuit, IC)。它的制造过程是人类智慧和工程技术的结晶,其复杂和精确程度令人叹为观止。本文将带你走进神秘的芯片制造工厂(Fab),了解一粒沙子是如何经历“七十二变”,最终成为驱动我们现代生活的智能核心。

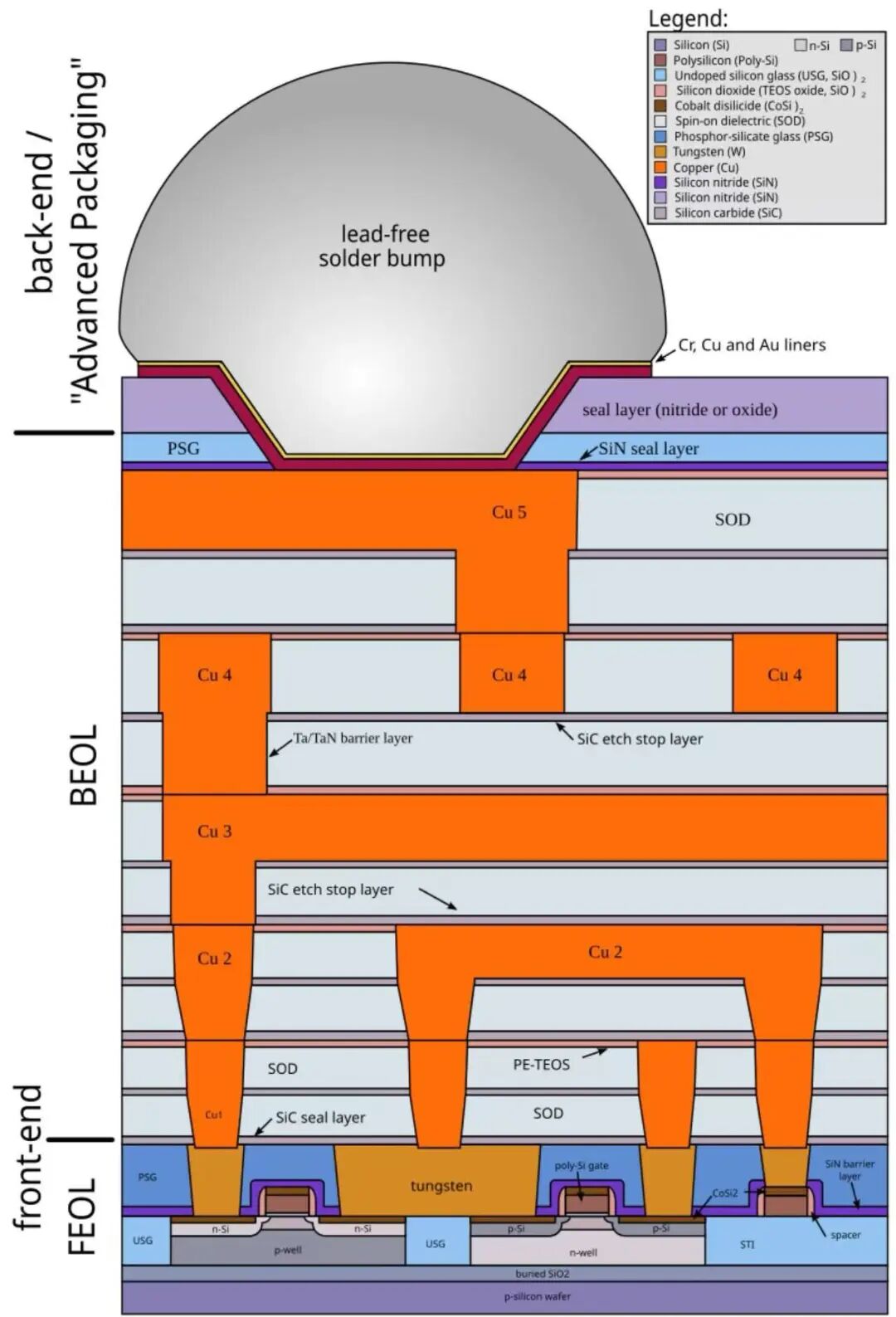

整个芯片制造流程极其复杂,可以概括为三大阶段:硅片制造、晶圆厂前道工序(Front-End-of-Line, FEOL)、晶圆厂后道工序(Back-End-of-Line, BEOL),以及最后的封装与测试。

第一阶段:基础构建 - 硅片制造

万丈高楼平地起,芯片的“地基”是高纯度的硅片,也称为晶圆(Wafer)。

1.原料提纯:芯片的起始原料是沙子(主要成分是二氧化硅 SiO₂)。沙子经过高温冶炼和化学方法,被提纯成纯度高达99.999999999%(9个9到11个9)的电子级多晶硅。这种纯度意味着每十亿个原子中,最多只允许有一个杂质原子。

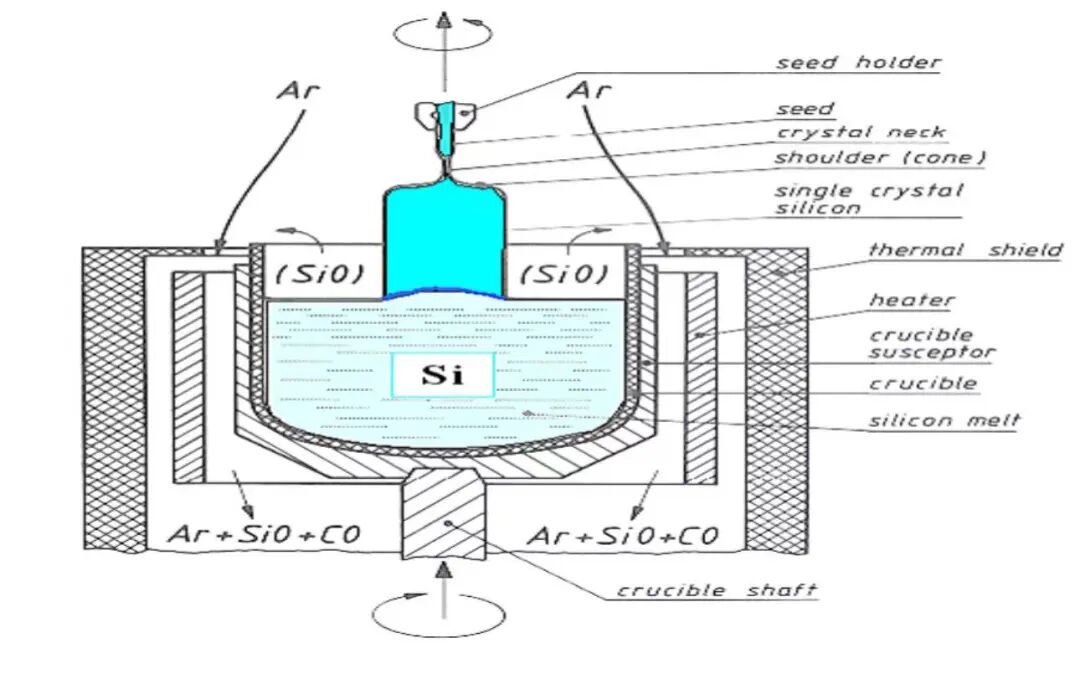

2.长晶与切割:将高纯度多晶硅放入石英坩埚中,在高温下熔化。然后,以一颗单晶硅的“籽晶”作为引导,通过精密的控制,缓慢地旋转并向上提拉,生长成一根巨大的、具有完美原子排列的圆柱形单晶硅锭(Ingot)。这个过程被称为“柴氏法”(Czochralski method)。

3.晶圆成型:接下来,巨大的单晶硅锭被用内部涂有金刚石的线锯精确地切割成厚度不足1毫米的薄片,这就是晶圆。之后,晶圆的边缘会被打磨成圆形,并在特定位置加工出缺口(Notch)或平边(Flat),用于在后续生产中定位。最后,晶圆片会经过化学机械抛光(CMP),使其表面达到原子级的平整和光滑,像镜面一样。

第二阶段:核心构建 - 前道工序

这是在晶圆上真正“雕刻”晶体管等纳米级元器件的过程,也是技术含量最高、最复杂的部分。整个过程在一个被称为“洁净室”(Cleanroom)的环境中进行,其洁净度比医院手术室还要高出数千甚至数万倍,以防止微尘颗粒影响芯片的良率。前道工序的核心是光刻(Photolithography),并辅以刻蚀、薄膜沉积和离子注入等步骤,循环往复,层层叠加。

1.薄膜沉积 (Deposition):首先,根据设计需要在晶圆表面生长或沉积一层特定的薄膜材料,例如二氧化硅(绝缘层)或氮化硅等。这可以通过热氧化(将晶圆置于高温氧气或水蒸气环境中)或化学气相沉积(CVD)等方法实现。

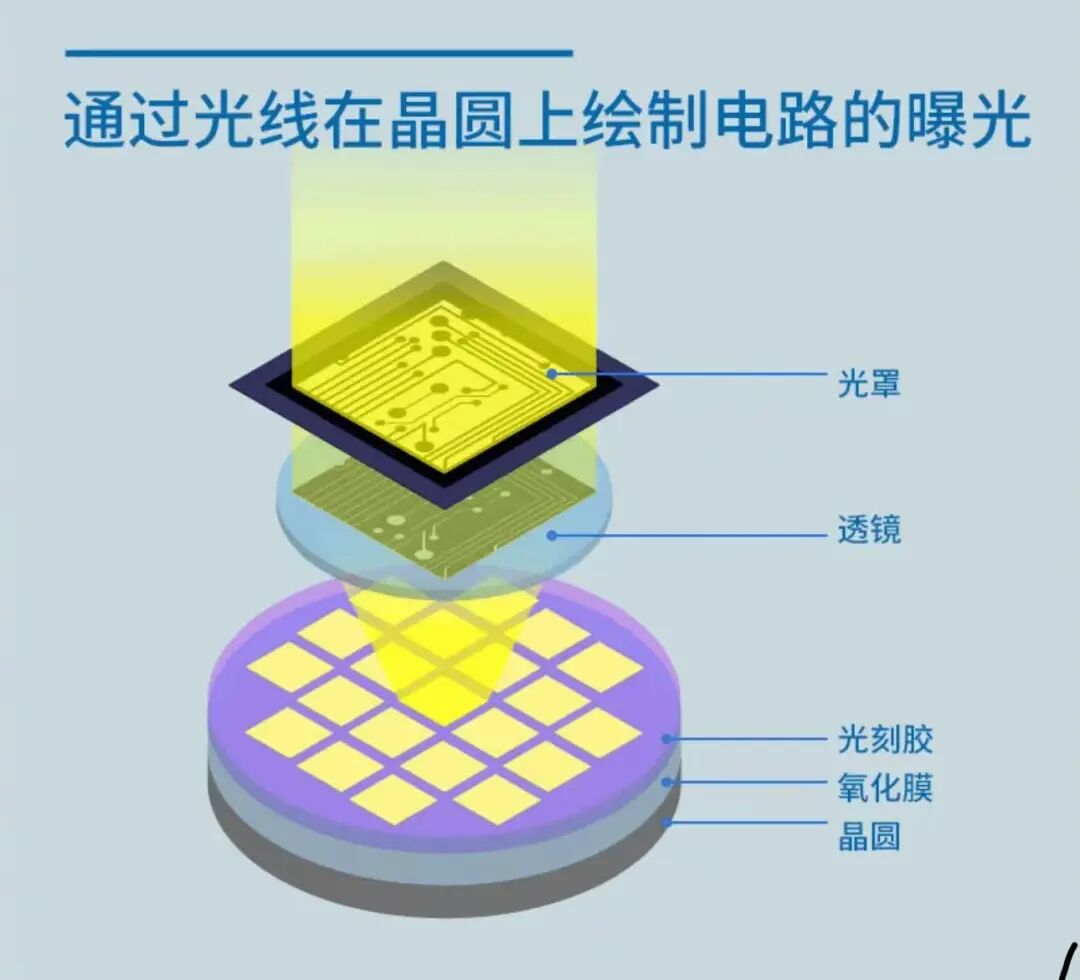

2.涂胶 (Coating):在薄膜上均匀地旋涂一层对特定波长的光敏感的化学物质——光刻胶(Photoresist)。3.光刻 (Photolithography) / 曝光 (Exposure):这是整个芯片制造中最关键、最昂贵的步骤。它就像用投影仪和胶片“拍照”。

4.掩膜版 (Mask/Reticle):首先,工程师会将设计好的芯片电路图案制作成一块高精度的石英玻璃板,这就是掩膜版。

5.曝光:然后,用极紫外光(EUV)或深紫外光(DUV)作为光源,穿过掩膜版,将电路图案精确地投射到涂有光刻胶的晶圆表面。被光照射到的光刻胶会发生化学性质的改变。

6.显影 (Development):用特定的化学溶剂清洗晶圆,被光(或未被光,取决于光刻胶是正性还是负性)照射过的光刻胶被溶解和去除,这样,掩膜版上的电路图案就“复印”到了光刻胶层上。

7.刻蚀 (Etching):刻蚀就像是“雕刻”。以留下的光刻胶图案为保护层,使用化学气体(等离子体刻蚀)或液体(湿法刻蚀)剥离掉没有被光刻胶覆盖的薄膜区域,从而将电路图案永久地刻在下方的薄膜上。

8.去除光刻胶:完成刻蚀后,用化学方法剥离掉剩余的光刻胶,晶圆上就留下了所需的第一层电路图案。

9.离子注入 (Ion Implantation):为了改变特定区域硅的导电性能(形成N型或P型半导体),需要将预先选定的杂质原子(如硼、磷)加速到极高的能量,像子弹一样注入到晶圆的特定区域。这一步是制造晶体管“源极”和“漏极”的关键。上述“沉积-涂胶-曝光-显影-刻蚀-注入”的流程会重复几十甚至上百次,每一次都制作一层新的电路图案,层层叠加,最终在晶圆上构建出包含数十亿个晶体管的复杂三维结构。

第三阶段:互联构建 - 后道工序

如果说前道工序是在“盖房子”,那么后道工序就是在“铺设房子的水电管网和通信线路”。它负责制造金属导线,将前道工序中制作出的亿万个晶体管按照电路设计图连接起来,形成一个完整的电路网络。

1.金属互连 (Metallization):这个过程通常采用“铜制程”(Copper Interconnect)。首先在晶圆表面沉积一层绝缘介质(通常是低k电介质,以减少信号延迟),然后通过光刻和刻蚀在介质上刻出沟槽(Trench)和通孔(Via)。

2.电镀铜:接着,使用电化学沉积(ECD)的方法,将铜原子填充到这些沟槽和通孔中。

3.化学机械抛光 (CMP):最后,再次使用CMP技术,将晶圆表面多余的铜磨平,只留下嵌入在绝缘介质中的铜导线。

这个过程同样需要重复多层,形成一个极其复杂的多层金属互连网络,确保信号可以在不同晶体管之间高速、准确地传输。

第四阶段:封装与测试

经过数百道工序后,一张晶圆上已经制造出了数百个完全相同的芯片单元,称为“裸片”(Die)。

1.晶圆测试 (Wafer Probing):在将晶圆切割成单个芯片之前,会用带有数千根探针的测试机对每个裸片进行电学性能测试,筛选出不合格的产品。

2.切割 (Dicing):用精密的金刚石刀轮沿着预设的切割道将晶圆切割成独立的裸片。

3.封装 (Packaging):合格的裸片非常脆弱,无法直接焊接到电路板上。封装过程就是为裸片制作一个保护性的外壳,并引出管脚,以便与外部电路连接。

4.贴片 (Die Attach):将裸片固定到封装基板(Substrate)上。

5.引线键合 (Wire Bonding):用极细的金线或铜线,将裸片上的焊点(Pad)与封装基板上的引脚连接起来。更先进的技术如倒装芯片(Flip-chip)则通过微小的焊球(Bumps)直接连接。

6.塑封 (Molding):用环氧树脂将整个结构包裹起来,形成我们最终看到的黑色芯片外观。

7.最终测试 (Final Test):封装完成后,会对芯片进行全面的功能、性能和可靠性测试,确保其在各种工作条件下(如不同温度、电压)都能正常工作。只有通过所有测试的芯片,才会被打上型号和批次,送往电子产品制造商手中。

从平凡的沙子到驱动信息时代的强大引擎,芯片的诞生是一段漫长而精密的旅程。它融合了物理、化学、光学、材料科学和精密机械等多个领域的顶尖技术。每一个环节的精度都以纳米(十亿分之一米)来衡量,任何一个微小的瑕疵都可能导致整个芯片的报废。正是这种对极致精密的追求,才使得人类能够不断突破计算能力的极限,创造出更加智能和便捷的未来。

在线留言询价

一文了解逻辑芯片和处理器芯片的关系

科技部长阴和俊:芯片攻关取得新突破!

一文了解闪存芯片和ROM关系

- 一周热料

- 紧缺物料秒杀

| 型号 | 品牌 | 询价 |

|---|---|---|

| TL431ACLPR | Texas Instruments | |

| RB751G-40T2R | ROHM Semiconductor | |

| CDZVT2R20B | ROHM Semiconductor | |

| BD71847AMWV-E2 | ROHM Semiconductor | |

| MC33074DR2G | onsemi |

| 型号 | 品牌 | 抢购 |

|---|---|---|

| TPS63050YFFR | Texas Instruments | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| BP3621 | ROHM Semiconductor | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| ESR03EZPJ151 | ROHM Semiconductor | |

| STM32F429IGT6 | STMicroelectronics |

AMEYA360公众号二维码

识别二维码,即可关注

请输入下方图片中的验证码: