- Ameya360 Component Supply Platform >

- Trade news >

- 浅析PCB射频电路四大基础特性

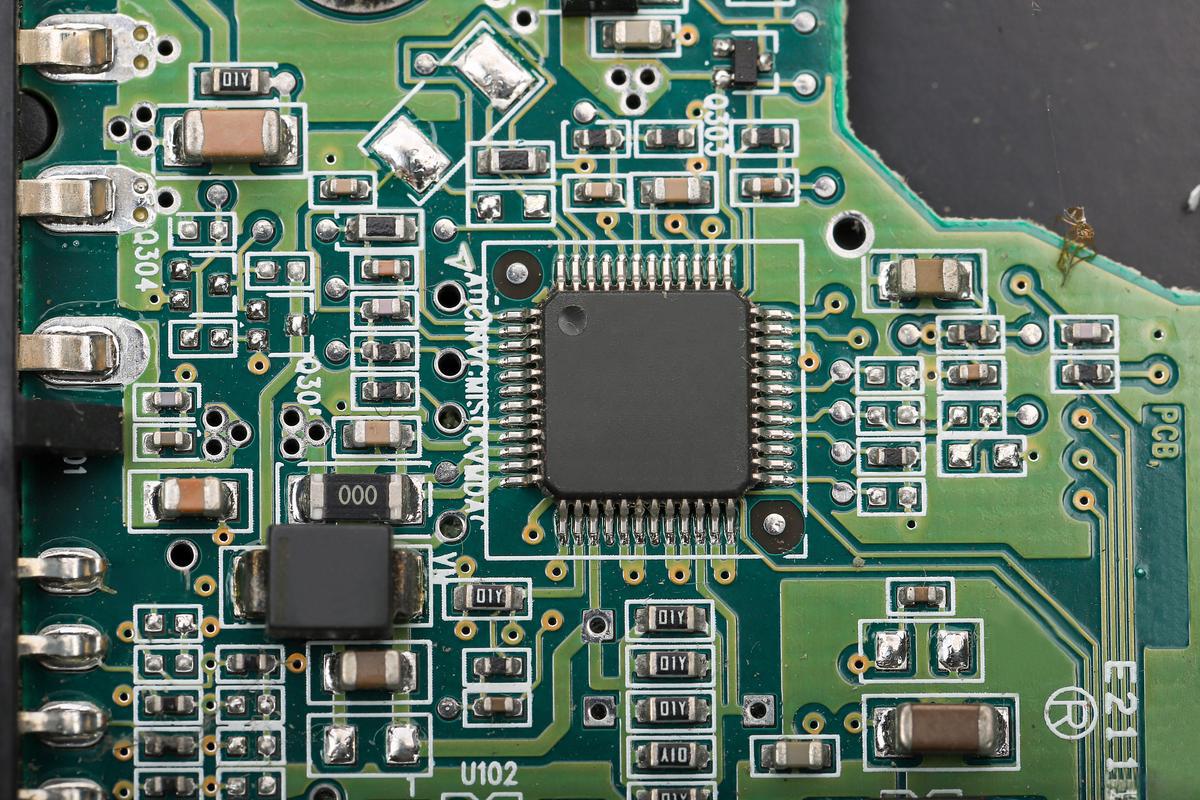

浅析PCB射频电路四大基础特性

射频简称RF。射频就是射频电流,它是一种高频交流变化电磁波的简称。每秒变化小于1000次的交流电称为低频电流,大于10000次的称为高频电流,而射频就是这样一种高频电流。射频是指射频电路产生的特定频率的调制电波。射频电路是指从天线(ANT)到收、发基带信号(RXI/Q、TXI/Q)为止的这部分电路。本文Ameya360电子元器件采购网从射频界面、小的期望信号、大的干扰信号、相邻频道的干扰四个方面解读射频电路4大基础特性,并给出了在PCB设计过程中需要特别注意的重要因素。

一、射频电路仿真之射频的界面

无线发射器和接收器在概念上,可分为基频与射频两个部份。基频包含发射器的输入信号之频率范围,也包含接收器的输出信号之频率范围。基频的频宽决定了数据在系统中可流动的基本速率。基频是用来改善数据流的可靠度,并在特定的数据传输率之下,减少发射器施加在传输媒介(transmission medium)的负荷。因此,PCB设计基频电路时,需要大量的信号处理工程知识。发射器的射频电路能将已处理过的基频信号转换、升频至指定的频道中,并将此信号注入至传输媒体中。相反的,接收器的射频电路能自传输媒体中取得信号,并转换、降频成基频。

发射器有两个主要的PCB设计目标:第一是它们必须尽可能在消耗最少功率的情况下,发射特定的功率。第二是它们不能干扰相邻频道内的收发机之正常运作。就接收器而言,有三个主要的PCB设计目标:首先,它们必须准确地还原小信号;第二,它们必须能去除期望频道以外的干扰信号;最后一点与发射器一样,它们消耗的功率必须很小。

二、射频电路仿真之大的干扰信号

接收器必须对小的信号很灵敏,即使有大的干扰信号(阻挡物)存在时。这种情况出现在尝试接收一个微弱或远距的发射信号,而其附近有强大的发射器在相邻频道中广播。干扰信号可能比期待信号大60~70 dB,且可以在接收器的输入阶段以大量覆盖的方式,或使接收器在输入阶段产生过多的噪声量,来阻断正常信号的接收。如果接收器在输入阶段,被干扰源驱使进入非线性的区域,上述的那两个问题就会发生。为避免这些问题,接收器的前端必须是非常线性的。

因此,“线性”也是PCB设计接收器时的一个重要考虑因素。由于接收器是窄频电路,所以非线性是以测量“交调失真(intermodulation distortion)”来统计的。这牵涉到利用两个频率相近,并位于中心频带内(in band)的正弦波或余弦波来驱动输入信号,然后再测量其交互调变的乘积。大体而言,SPICE是一种耗时耗成本的仿真软件,因为它必须执行许多次的循环运算以后,才能得到所需要的频率分辨率,以了解失真的情形。

三、射频电路仿真之小的期望信号

接收器必须很灵敏地侦测到小的输入信号。一般而言,接收器的输入功率可以小到1 μV。接收器的灵敏度被它的输入电路所产生的噪声所限制。因此,噪声是PCB设计接收器时的一个重要考虑因素。而且,具备以仿真工具来预测噪声的能力是不可或缺的。附图一是一个典型的超外差(superheterodyne)接收器。接收到的信号先经过滤波,再以低噪声放大器(LNA)将输入信号放大。然后利用第一个本地振荡器(LO)与此信号混合,以使此信号转换成中频(IF)。前端(front-end)电路的噪声效能主要取决于LNA、混合器(mixer)和LO。虽然使用传统的SPICE噪声分析,可以寻找到LNA的噪声,但对于混合器和LO而言,它却是无用的,因为在这些区块中的噪声,会被很大的LO信号严重地影响。

小的输入信号要求接收器必须具有极大的放大功能,通常需要120 dB这么高的增益。在这么高的增益下,任何自输出端耦合(couple)回到输入端的信号都可能产生问题。使用超外差接收器架构的重要原因是,它可以将增益分布在数个频率里,以减少耦合的机率。这也使得第一个LO的频率与输入信号的频率不同,可以防止大的干扰信号“污染”到小的输入信号。

因为不同的理由,在一些无线通讯系统中,直接转换(direct conversion)或内差(homodyne)架构可以取代超外差架构。在此架构中,射频输入信号是在单一步骤下直接转换成基频,因此,大部份的增益都在基频中,而且LO与输入信号的频率相同。在这种情况下,必须了解少量耦合的影响力,并且必须建立起“杂散信号路径(stray signal path)”的详细模型,譬如:穿过基板(substrate)的耦合、封装脚位与焊线(bondwire)之间的耦合、和穿过电源线的耦合。

四、射频电路仿真之相邻频道的干扰

失真也在发射器中扮演着重要的角色。发射器在输出电路所产生的非线性,可能使传送信号的频宽散布于相邻的频道中。这种现象称为“频谱的再成长(spectral regrowth)”。在信号到达发射器的功率放大器(PA)之前,其频宽被限制着;但在PA内的“交调失真”会导致频宽再次增加。如果频宽增加的太多,发射器将无法符合其相邻频道的功率要求。当传送数字调变信号时,实际上,是无法用SPICE来预测频谱的再成长。因为大约有1000个数字符号(symbol)的传送作业必须被仿真,以求得代表性的频谱,并且还需要结合高频率的载波,这些将使SPICE的瞬态分析变得不切实际。

以上就是Ameya360电子元器件采购网关于PCB射频电路四大基础特性的所有内容介绍了,希望对大家有所帮助。

Online messageinquiry

中国大陆百家集成电路设计公司!

模拟电路设计中噪声分析的误区及注意事项

射频、低频、中频电路如何不互相干扰?

- Week of hot material

- Material in short supply seckilling

| model | brand | Quote |

|---|---|---|

| BD71847AMWV-E2 | ROHM Semiconductor | |

| MC33074DR2G | onsemi | |

| RB751G-40T2R | ROHM Semiconductor | |

| CDZVT2R20B | ROHM Semiconductor | |

| TL431ACLPR | Texas Instruments |

| model | brand | To snap up |

|---|---|---|

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| STM32F429IGT6 | STMicroelectronics | |

| TPS63050YFFR | Texas Instruments | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| BP3621 | ROHM Semiconductor | |

| ESR03EZPJ151 | ROHM Semiconductor |

Qr code of ameya360 official account

Identify TWO-DIMENSIONAL code, you can pay attention to

Please enter the verification code in the image below: